基本的半导体元件及原理

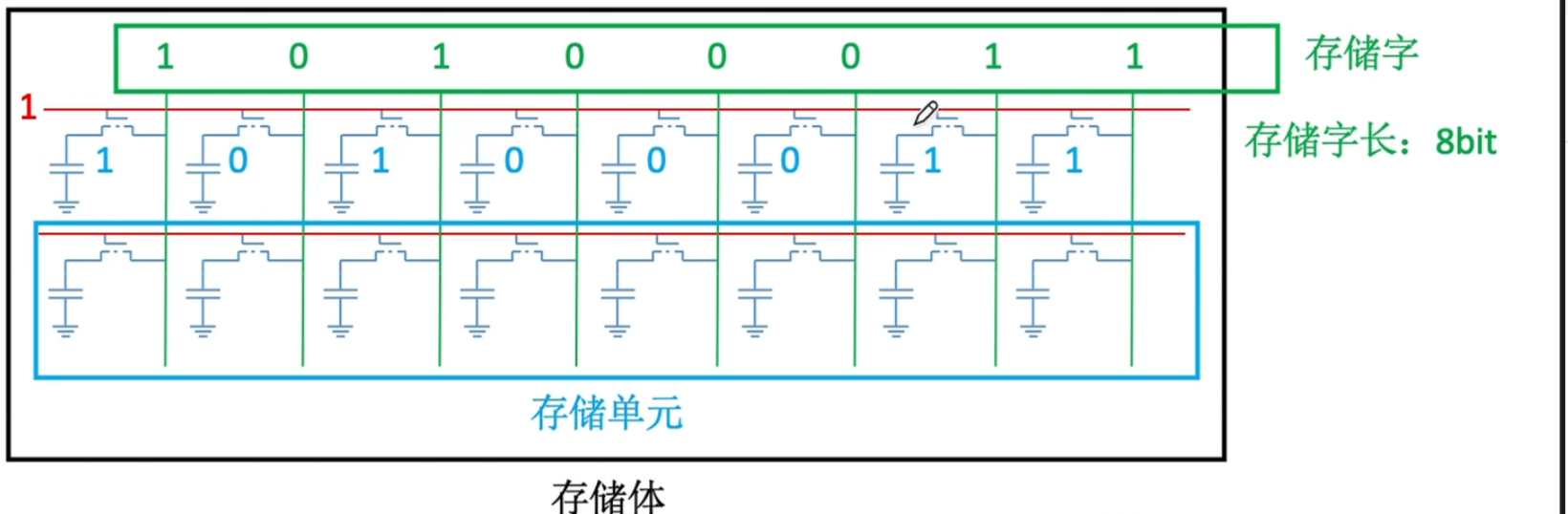

存储体中的数据由二进制来进行存储,而每一位都是一个存储元。存储元的结构如下图所示:

- MOS管:MOS管可理解为一种电控开关,输入电压达到某个阈值时,MOS管就可以连通

叫它半导体的原因就是,它既不是导体也不是半导体,给够足够电压才能连通。

原理:当我们上方给一个足够高的电压时候,电容上板电压会高,而下面是接地的,高电压差将会在电容器中间存储电荷,我们根据存储了多少电荷来判断二进制是否为1。

我们如果将多个存储元连接,那就可以存储一串二进制数据,如图:

这个红色的线连接了每个存储元的MOS管,如果红线是5V,那么所有MOS管都会连通,此时绿色的线处如果有电流,就为1,否则为0。

⭐存储器芯片的基本原理

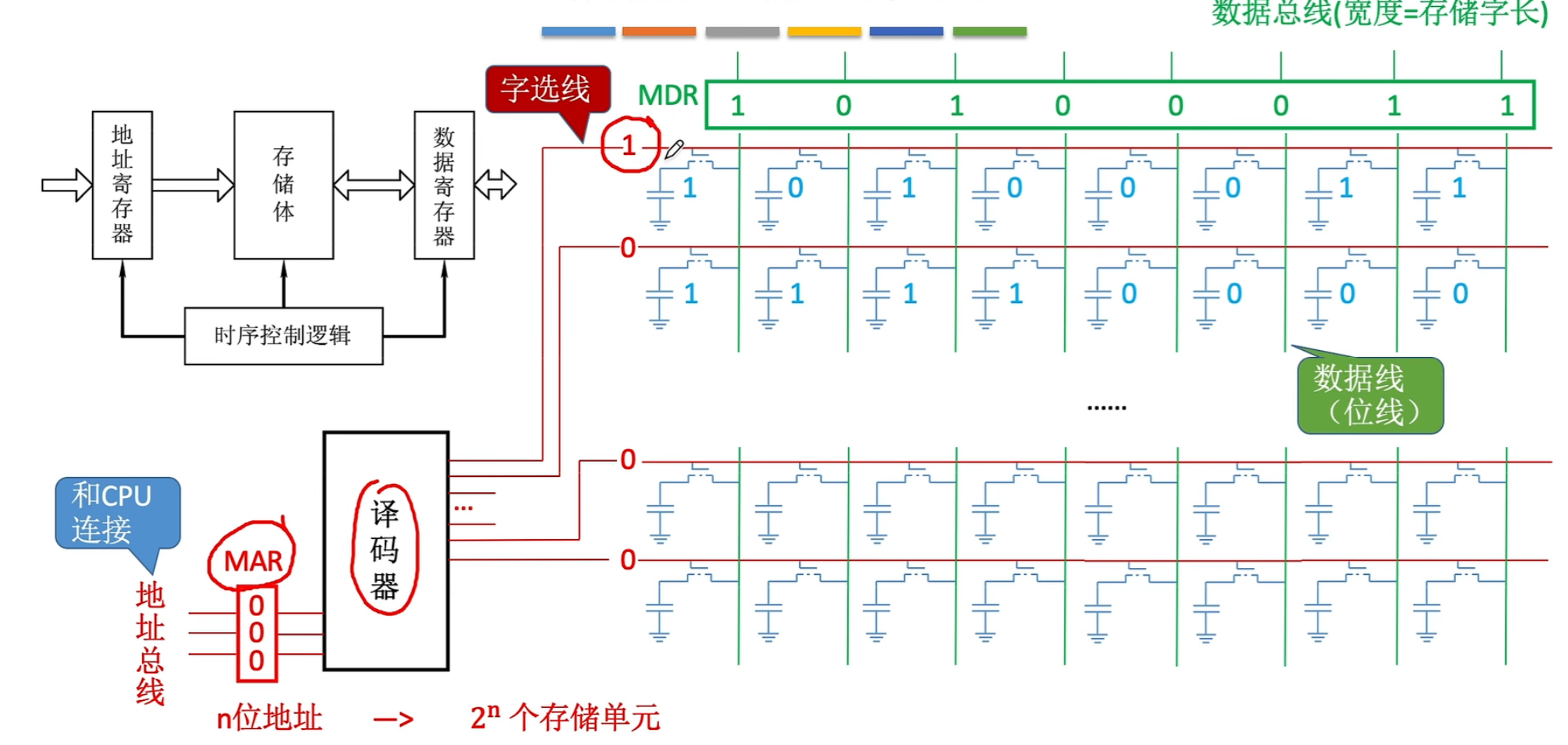

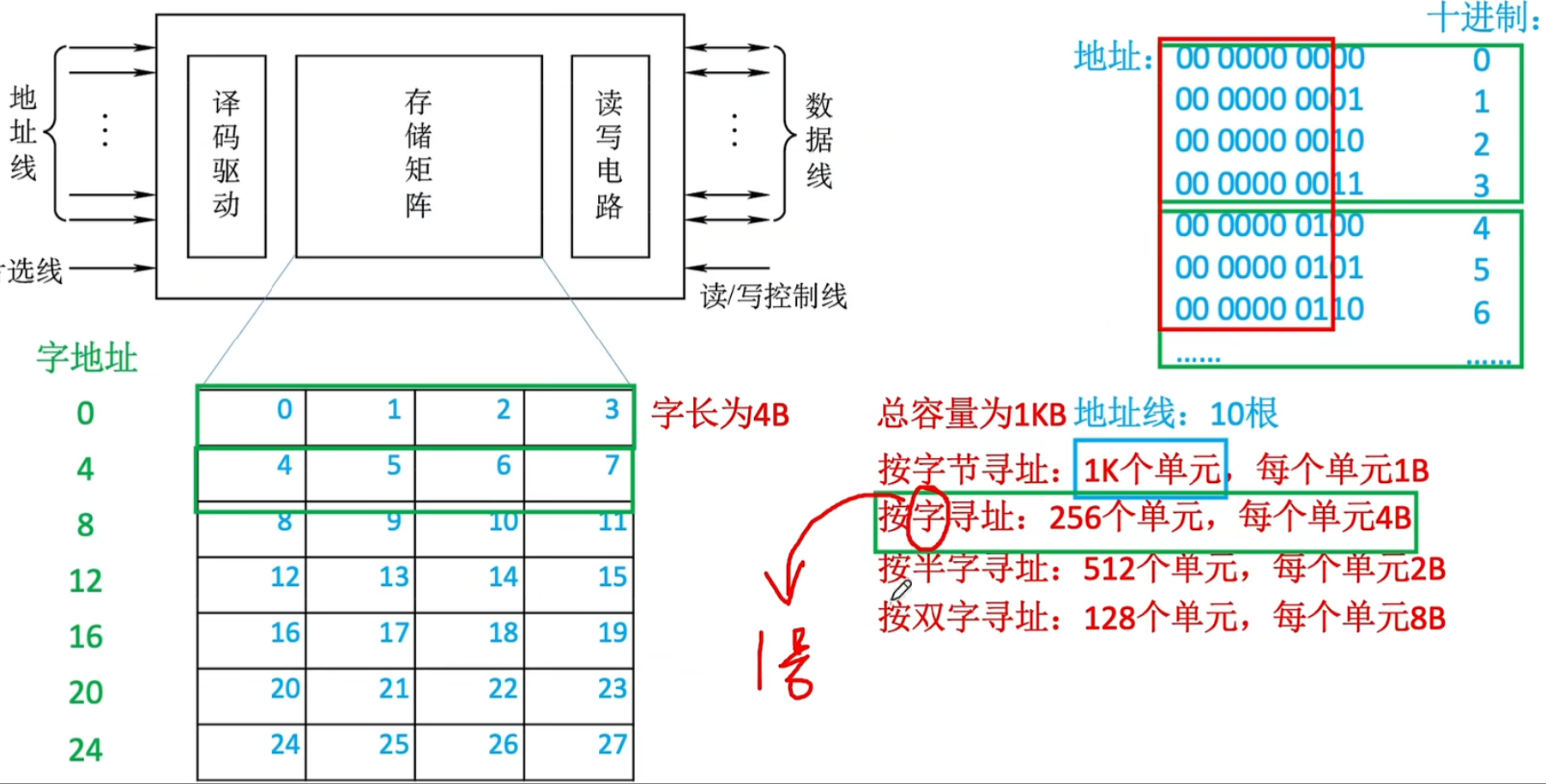

我们现在要了解如何根据地址来知道我们要读或者写哪个存储字呢?

这个时候我们就需要**译码器*的作用:

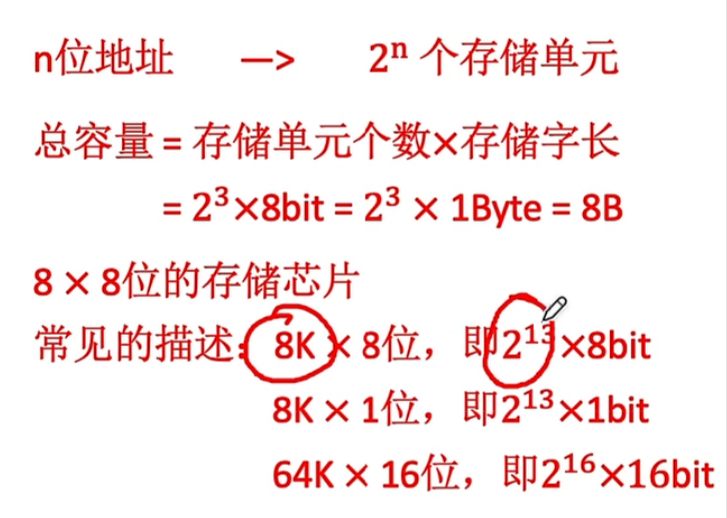

- 它能将n位地址–>$2^n$个存储单元

- 地址总线和CPU相同,将地址通过MAR给编码器

- 接着编码器根据地址选取字选线(也就是红色的线)

- 给该线高电压,就可以通过数据线(绿色)获取该字二进制

- 最后CPU通过数据总线取走整个字的数据

$$总容量=存储单元个数*存储字长=2^3*8Bit=2^3*1Byte=8B $$

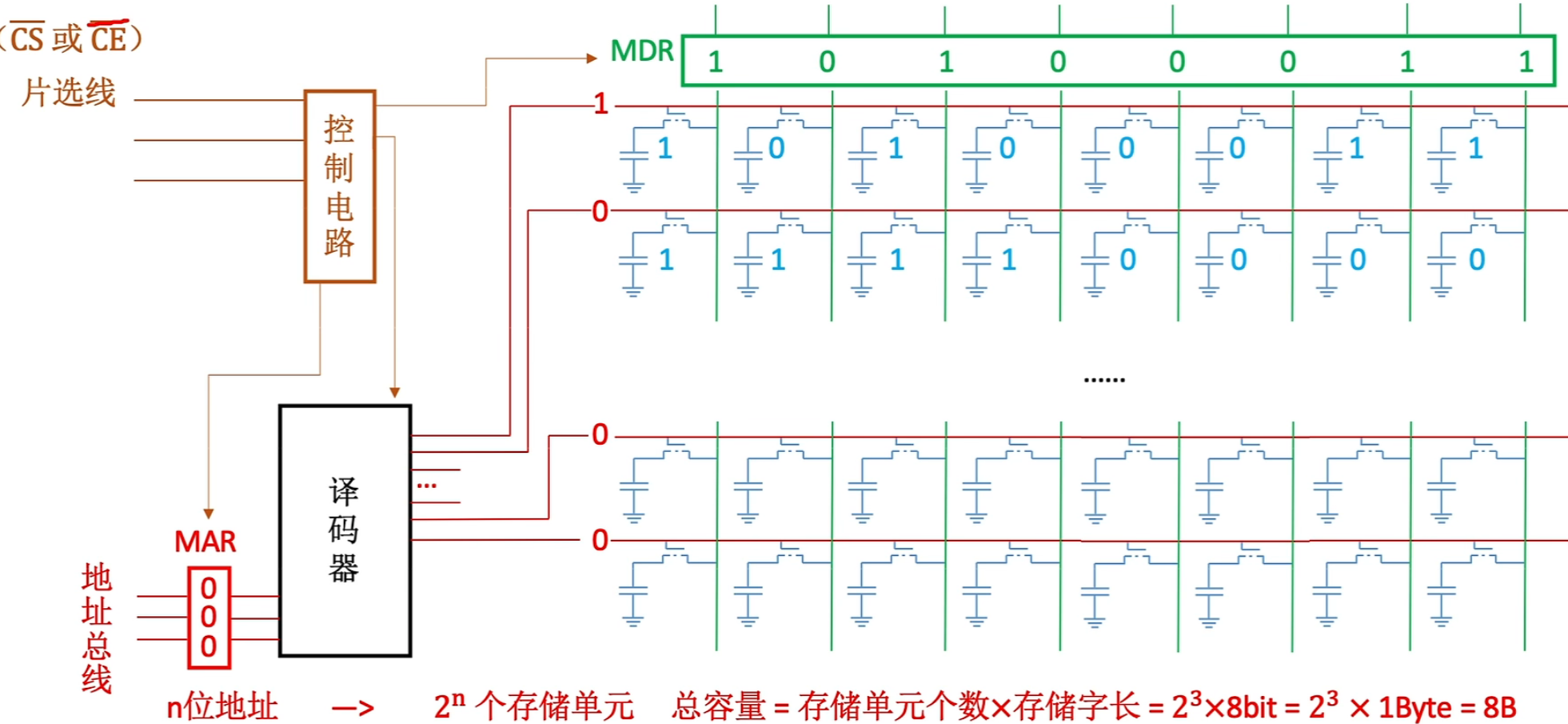

但我们还需要一点补充,由于MAR里面的电信号可能不稳定,所以我们还需要一个控制信号。 - 控制电路会先空值MAR,让MAR先稳定,接着将电信号再传给译码器。

- 然后通过控制电路来开关译码器。

- 只有当电信号稳定后,控制电路才会认为这个数据字是正确的。

另一个方面,控制电路也需要片选线的链接

- 片选线头上划线表示该信号低电平有效。

并且片选线下面那了条线分别是读控制线和写控制线: - 两根读/写线

- $\overline{WE}$允许写

- $\overline{OE}$允许读

- 一根读/写线

- $\overline{WE}$低电平写,高电平读

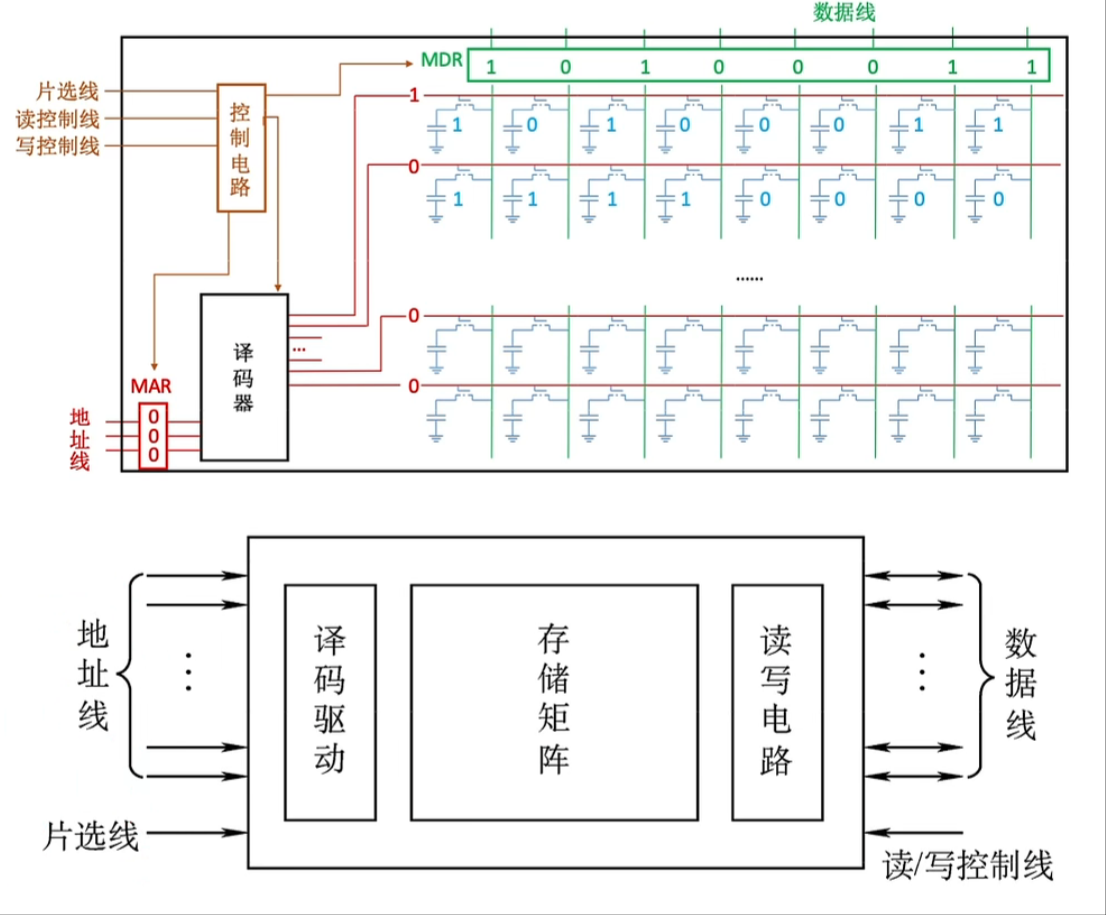

我们可以将其封装成如下图:

- $\overline{WE}$低电平写,高电平读

- 译码驱动:译码器加后面的一个驱动器,这个驱动器增强信号作用

- 读写线路:也就是控制电路和那些红红绿绿的线

- 片选线:读取存储矩阵中哪一个存储元件,这边用内存条来展示下:

这里每个黑黑的都是一个芯片,片选器就是选一个芯片来读,人如其名。并且内存条内有很多金属引脚,引脚的个数也就是地址线的个数,片选线,数据线,控制线的和

这里每个黑黑的都是一个芯片,片选器就是选一个芯片来读,人如其名。并且内存条内有很多金属引脚,引脚的个数也就是地址线的个数,片选线,数据线,控制线的和

之后我们还会遇到如下图的表示方法,前面的数字是存储单元,后面的是字长,记住就好:

寻址

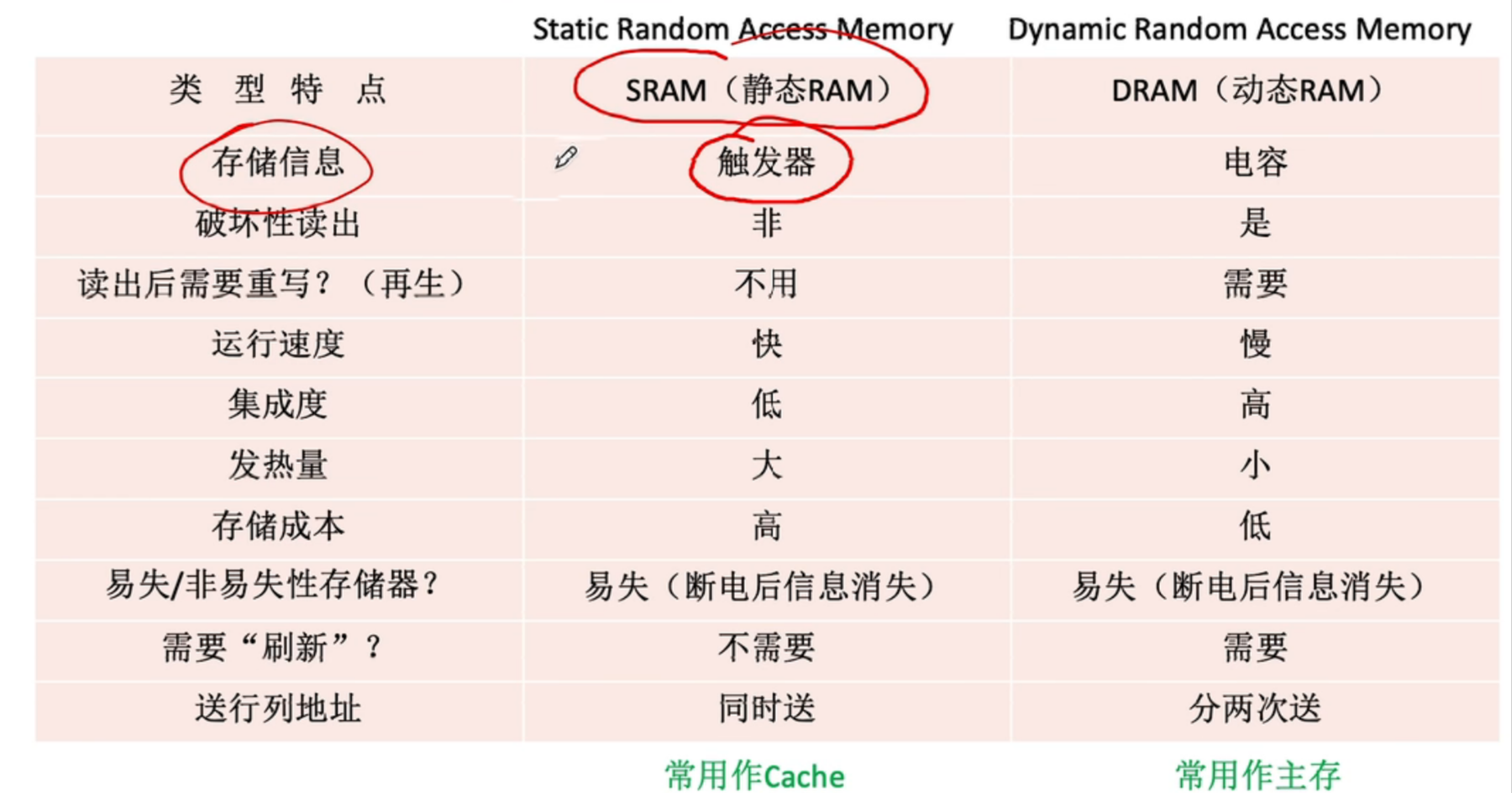

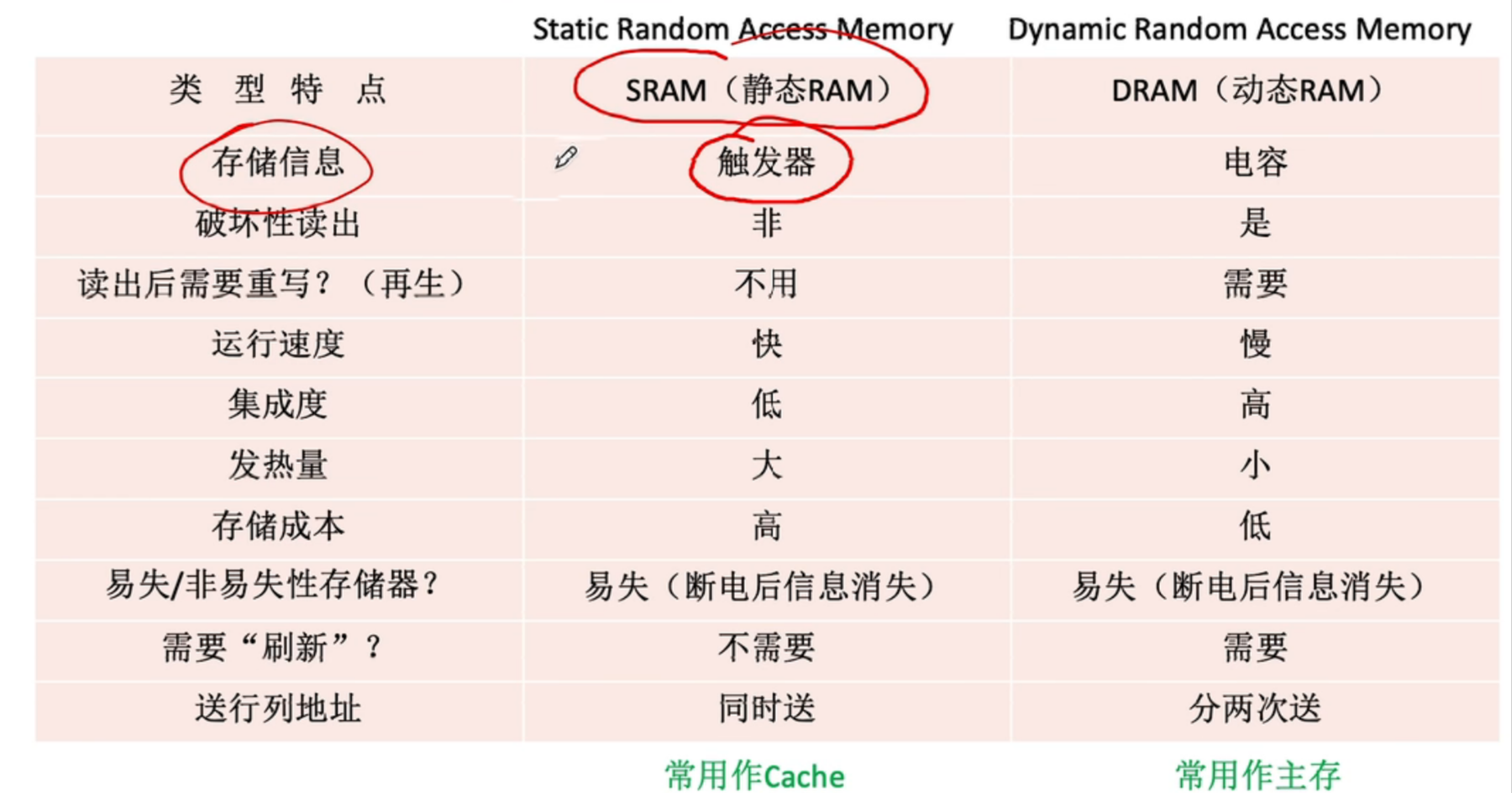

SRAM和DRAM

- Dynamic Random Access Memory ,即动态RAM

- Static Random Access Memory,即静态RAM

DRAM用于主存、SRAM用于Cache(高速缓冲存储器)

DRAM芯片

就是我们上一小节学到的芯片。

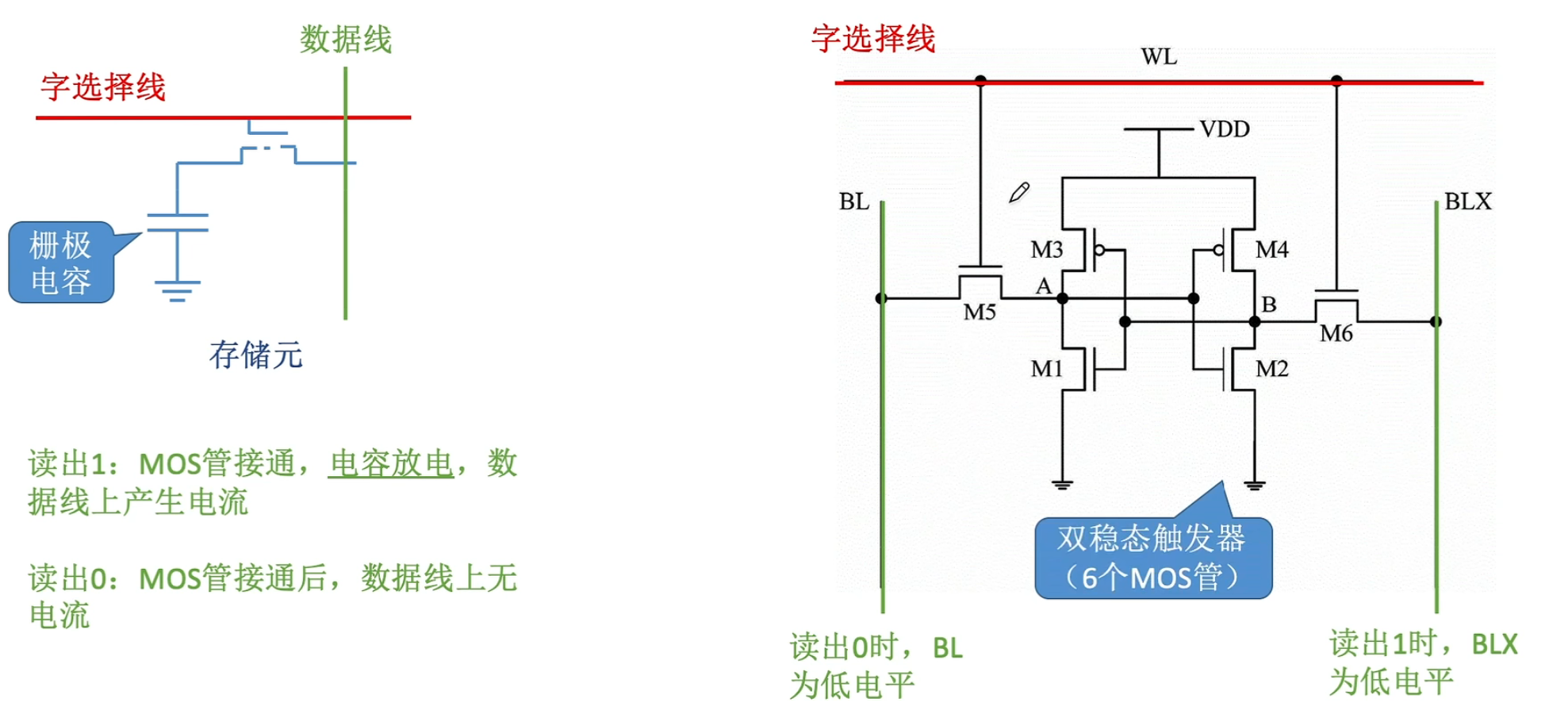

- DRAM芯片:使用栅极电容存储信息(就是上小节那一堆电容)

- SRAM芯片:使用双稳态触发器存储信息

核心区别:存储元不一样

栅极电容VS双稳态触发器

👈🏻栅极电容,👉🏻双稳态触发器

双稳态触发器我们这边只做了解,看下图就好了:

- 1:A高B低

- 0:A低B高

- 上面的是写入,读取的话就是给电压看BL和BLX谁输出电信号就行了

读写速度上

- 栅极电容:电容放电信息被破坏,是破坏性读出,付出后应有重写操作,也称再生。

- 双稳态触发器:读出数据,触发器状态保持稳定,是非破坏性读出,无需重写

由于栅极电容需要重写,而双稳态触发器不需要,所以读写速度上前者慢于后者。

成本上

- 栅极电容:每个存储元制造成本更低,集成度高,功耗低

- 双稳态触发器:每个存储元制造成本更高,集成度低,功耗大

总结

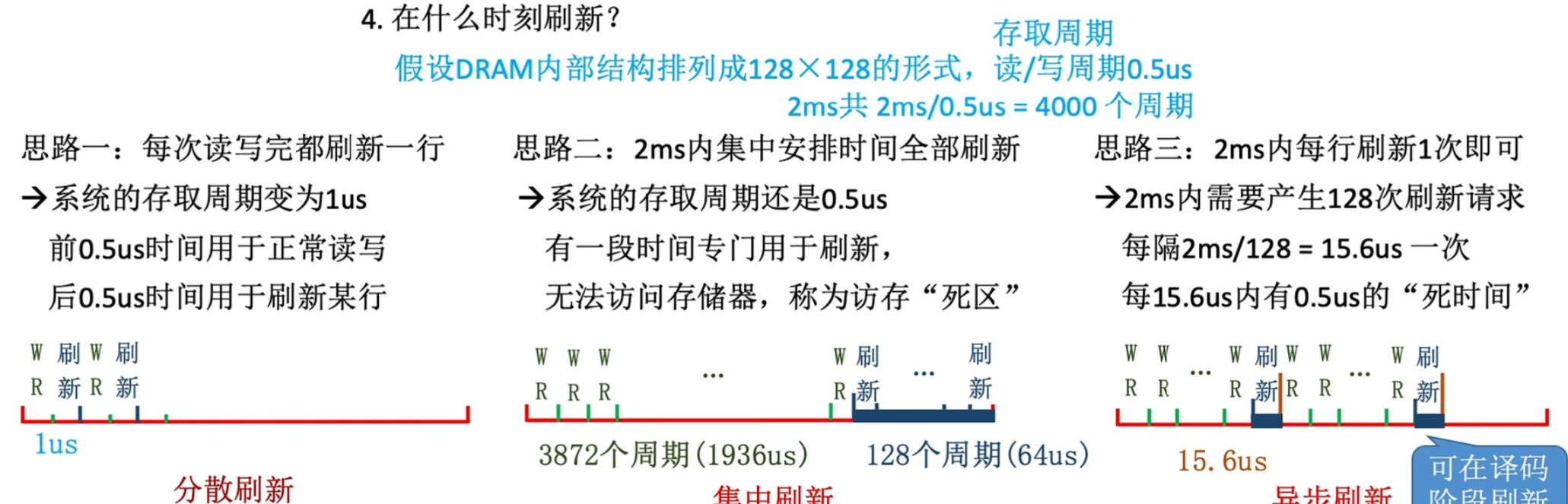

DRAM的刷新

由于电容不通电的情况下可能会自己慢慢流逝,导致二进制从0变成1之类的问题,所以为了避免丢失,我们需要一个操作叫做刷新,那么多久刷新一次呢,一般是2ms

- 多久刷新一次:2ms

- 每次刷新多少存储单元:以行为单位,每次刷新一行存储单元

- 如何刷新:有硬件(刷新电路)支持,读出一行的信息后重新存入,占用一个读/写周期

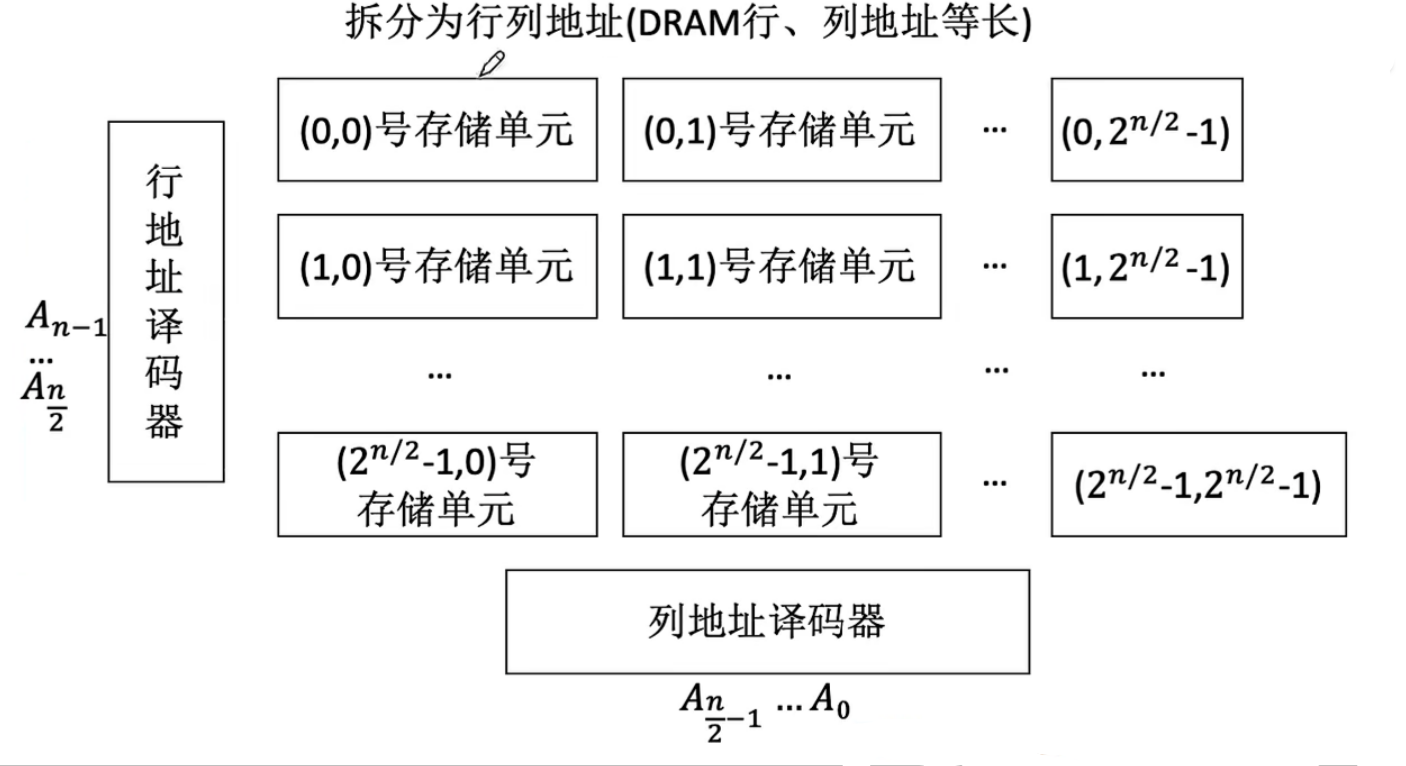

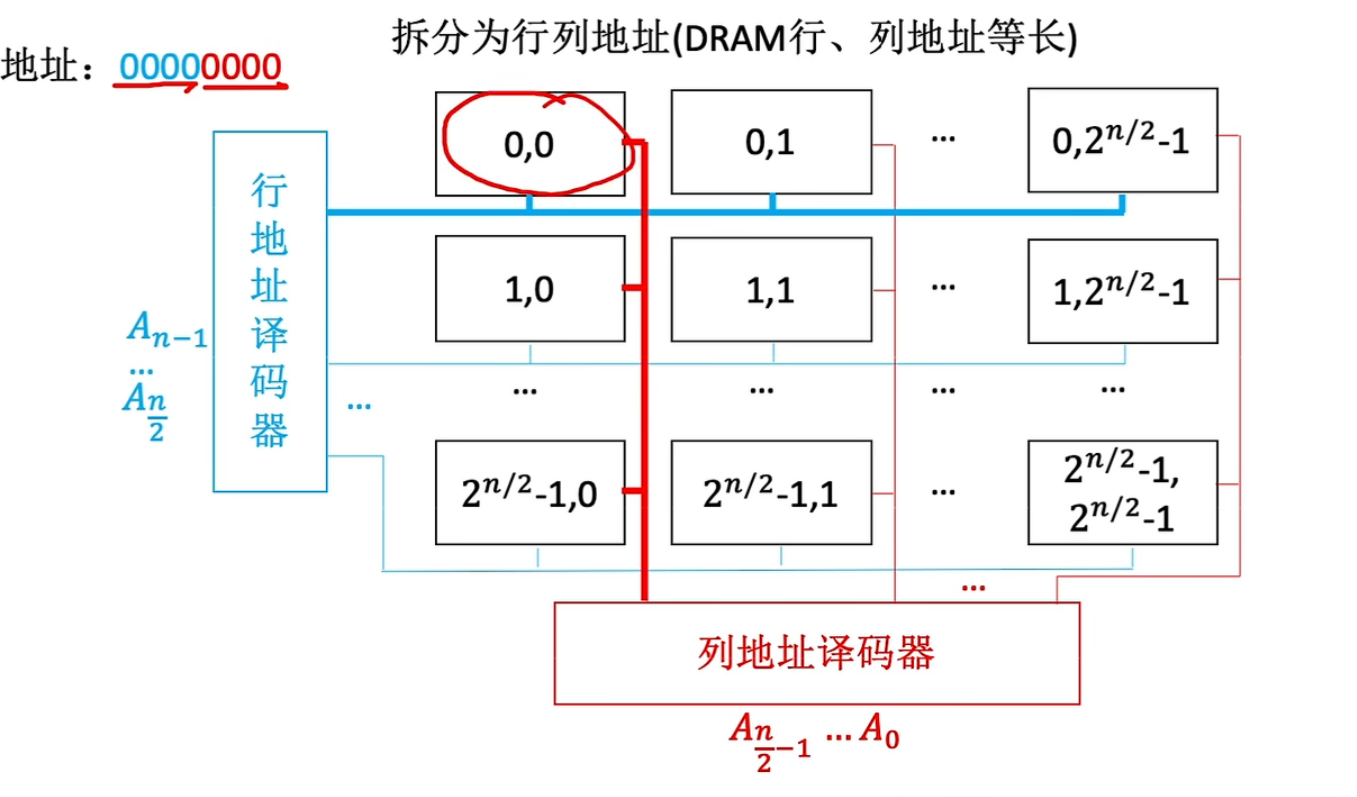

我们原来说,一个存储单元,对应一根译码器的线。如果译码器有n个线,那么就会有$2^n$个存储单元,这样会非常麻烦排线:

有一种解决方式就是把存储单元变成二维排列:

接着来讲解一下如何读取现代的DRAM行:

把地址分成两半,前面是行,后面是列。那么最后的最后我们来讨论下何时刷新:

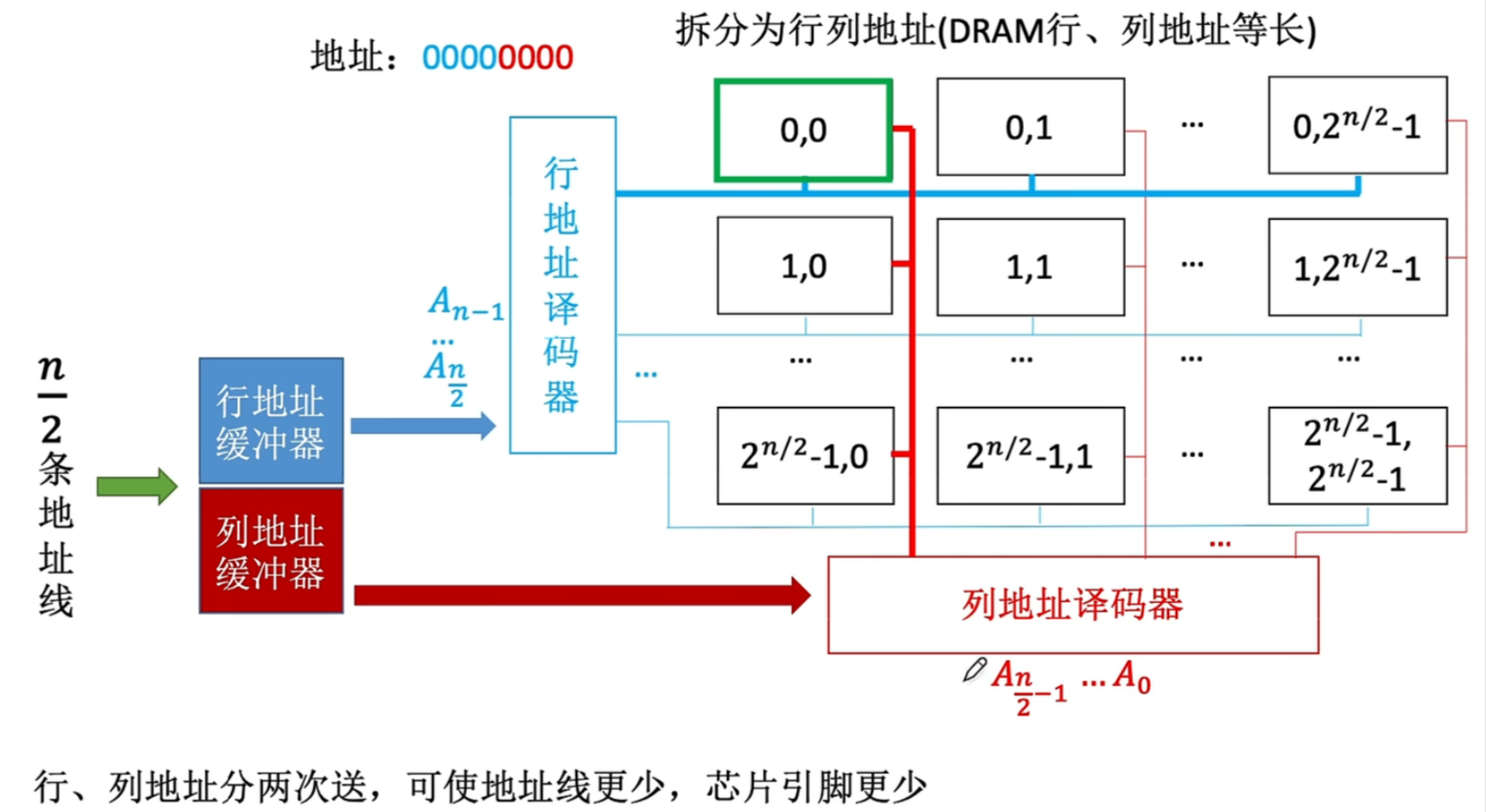

送行列地址的复用

DRAM地址线分两次送,可以有效减少地址线的数量: 这样子可以变成只使用n/2地址线,地址线减半也就意味着存储芯片上的金属引脚减半,节约成本。

这样子可以变成只使用n/2地址线,地址线减半也就意味着存储芯片上的金属引脚减半,节约成本。

说些什么吧!